NEWS

- 2025年8月5日

- 2025年8月5日

- 2025年7月30日NEDO『省エネAI半導体及びシステムに関する技術開発事業』成果報告会にて、NEDO事業「RISC-Vシステム設計プラットフォーム」の研究成果を発表します。

- 2025年7月23日

- 2025年6月20日

- 2025年6月17日

- 2025年6月17日RISC-V Design Center公式サイトを公開しました。

RISC-Vを

もっと自由に、もっと早く。

RISC-V Design Centerは

日本発・RISC-V設計のエコシステムを支える

専門団体です。

事業概要

RISC-V Design Center(RVDC)はオープン命令仕様のRISC-Vを基盤に、研究機関・アドバイザー・ハード/ソフトウェアベンダーと連携し、RISC-VコアおよびSoC設計資産を産業界に広く提供します。革新的な開発手法の共有を通じて、日本の半導体業界に新しい製品開発の流れを生み出します。

RVDCについて

産業のコメと言われる半導体ですが、昨今の半導体を使った電子・電機機器の殆どが、汎用のプロセッサを使用しています。

プロセッサの選択肢が限られてる製品開発では、自ずと似たような製品ばかりが市場に溢れてしまいます。

「あんな機能が作れたら」「こんな性能が出せたら」と製品企画では考えますが、そんな自由な発想を実現させるプロセッサは今まで在りませんでした。

さらに、プロセッサの中身を見れば、汎用プロセッサには、不必要な機能回路もたくさん載っているので、処理速度を速くしたり、消費電力を削減したりすることが困難でした。

プロセッサの中身が分からなかったり、改変出来ないライセンス契約だったりすることもあります。

「それならばオープン命令仕様のRISC-Vが有るじゃないか!」と思いますが、RISC-Vの公式サイトに行けば、プロセッサの仕様書が有るだけです。

仕方が無いから、結局RISC-V International に加盟しているベンダーに頼むことになります。欲しい機能や性能はIP購入や委託製作で実現出来ますが、支払う費用も掛かる時間もあまり変わらないと言う事態になってしまいます。

そして、設計した回路を検証する膨大な労力は、相変わらず必要になるのです。

RISC-Vの仕様全てがCコードで記述されていて、検証が済んでいる。

従来のverilogやSystemCに比べ、遥かに短い時間で設計/検証が出来るツールが有る。

この2つが揃えば、欲しい回路が自由に設計/検証出来るはずです。

日本におけるロジック半導体開発力の衰退を何とか止め、日本半導体業界の再興に寄与するため、NEDOプロジェクトを通して、RISC-Vデザインセンターは開設されることになりました。

――― 一般財団法人新システムビジョン

研究開発機構(NSV)

C言語化したオープン命令仕様のRISC-V(第5世代RISCプロセッサ)と全く新しい論理回路高位記述設計/検証環境である「C2RTL」を使って、最適化されたRISC-Vプロセッサを今までにない生産効率で設計/検証する手法を獲得する、学びと情報共有の場です。

RISC-Vデザインセンター(RVDC)は、東京科学大学集積Green-niX+研究ユニット内に設置された、商業的利益を目的とした団体ではない非営利組織であり、記載されている参加プラン費用は、RVDCの運営経費に充てられます。

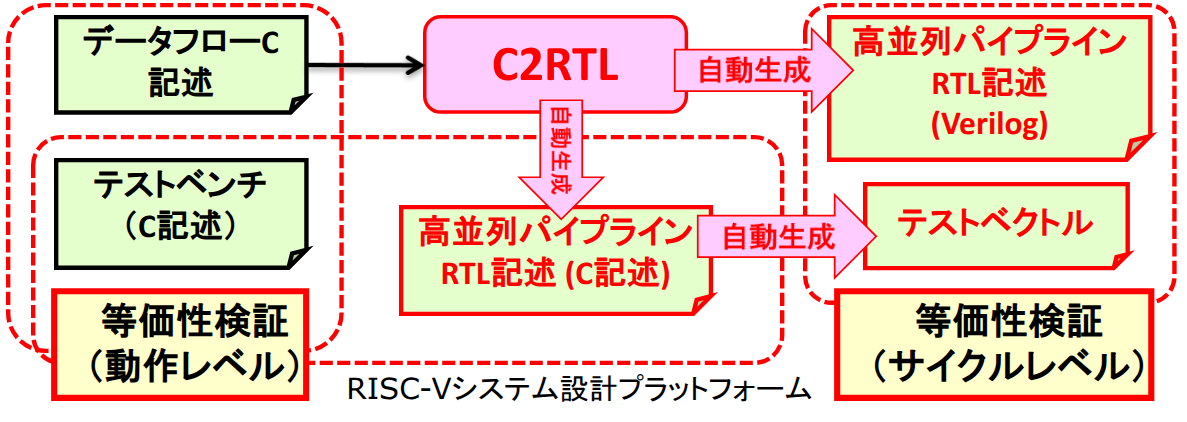

C2RTLは、ソフトウェア記述によるデータフローをそのままハードウェア、RTLに変換する技術です。

C/C++によるサイクルレベル記述により、プロセッサや深層学習などの並列処理が簡単に表現、実装することができ、

またソフトウェア環境でハードウェアシミュレーションを行うことが可能で、効率的な検証を行うことができます。

C2RTL概要

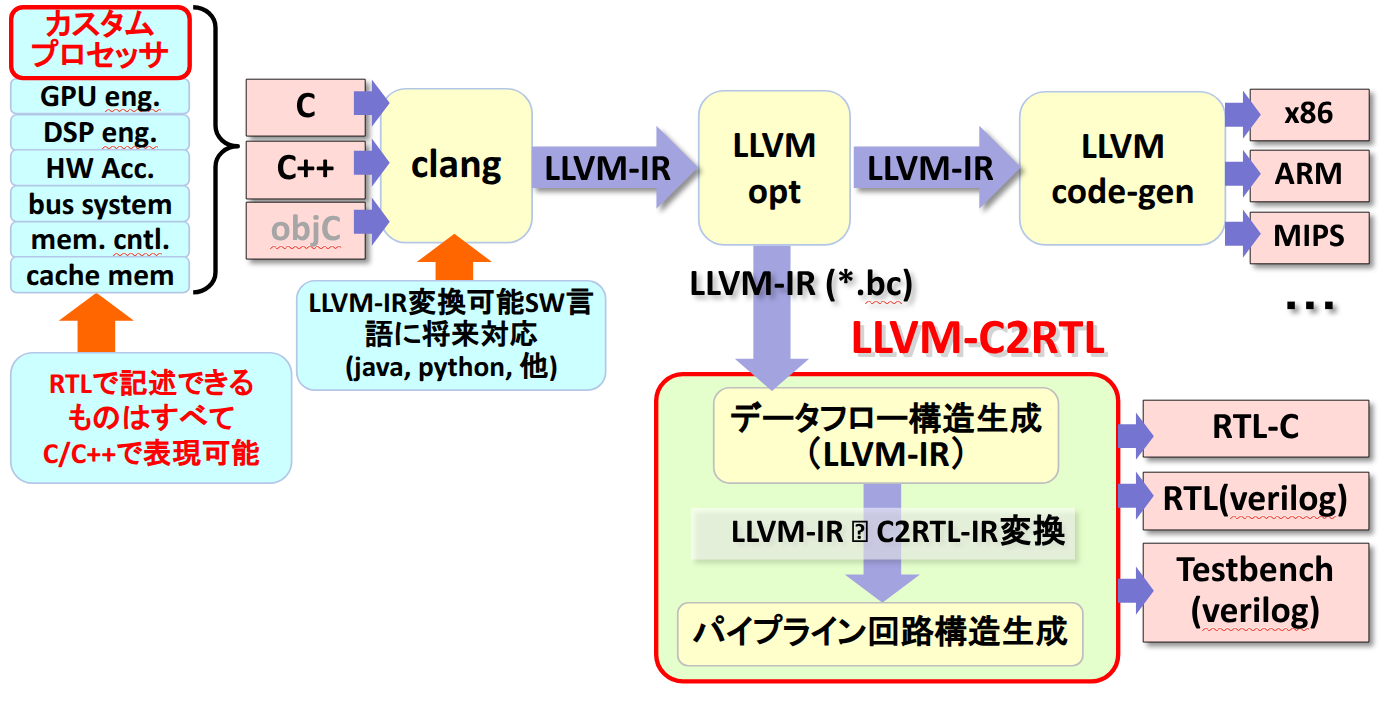

LLVM-C2RTL概要

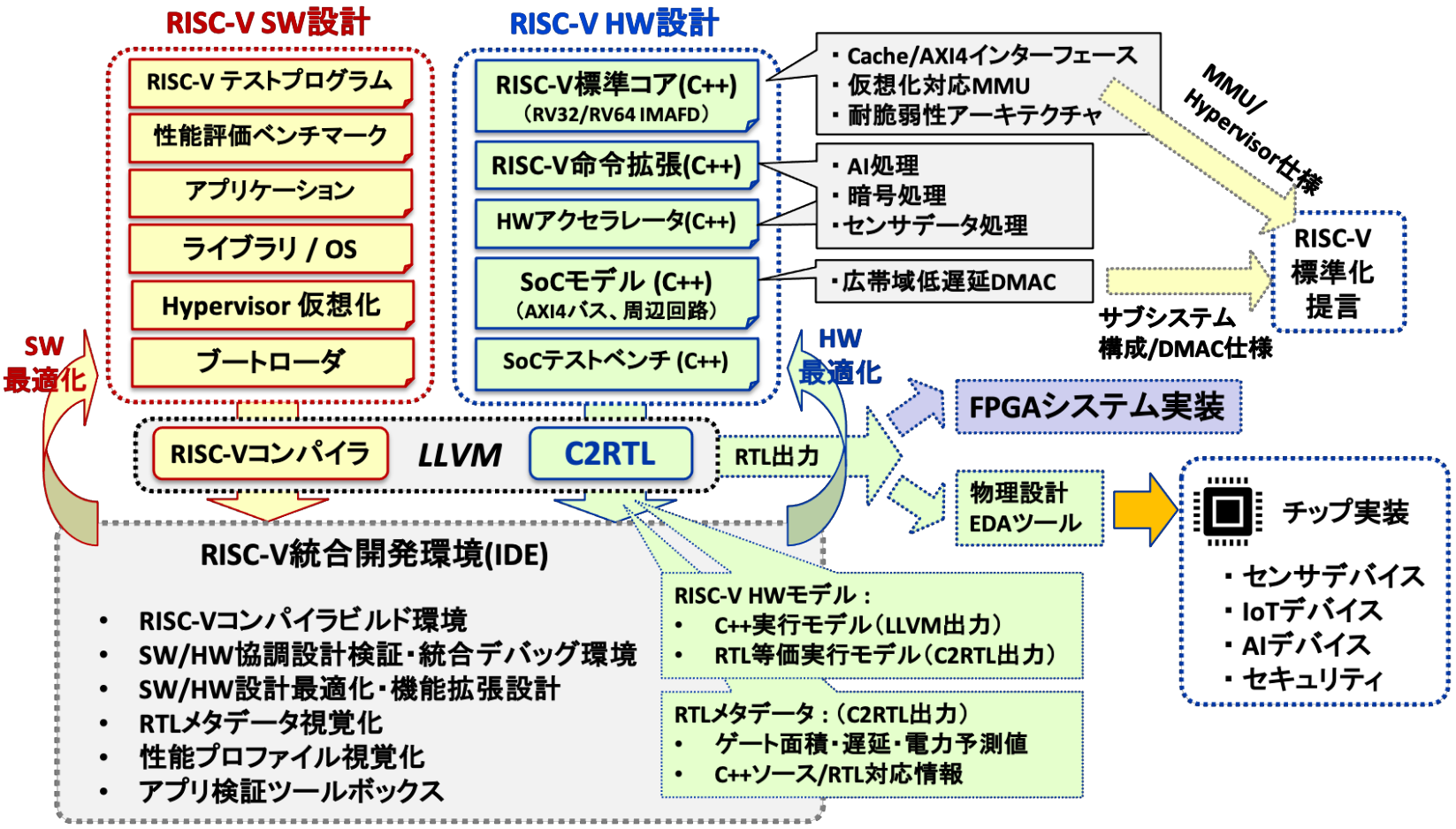

RISC-V HW/SW統合開発環境

C2RTLとは、C/C++言語だけでロジック半導体を設計・検証し、RTLを自動生成できる日本発の設計/検証環境です。

RISC-V デザインセンターに参加するには?

お問い合わせにて参加申し込みをお願いいたします。

お申し込み内容を事務局が確認し、参加承認に関するご連絡を差し上げます。

参加承認のご連絡を受け取った後、指定の口座へ参加費用をお振込みください。

お振込みが確認でき次第、開発環境やRISC-Vリソースなどの詳細に関するご連絡を差し上げます。

正規版C2RTLは、株式会社NSVTから直接提供されますのでRVDCとは別契約となります。

正規版C2RTLの契約者は、事務局へ直接RVDC参加申請をするだけで、追加費用なしで、Type2ユーザーとなる事が出来ます。

(C2RTL正規版のご契約は事務局までお問い合わせください)

お試し評価期間

1ヶ月無料

評価サーバ内でのご試用になります(RTL生成物はダウンロードいただけません)。

ユーザ樣のご要望に応じて、C2RTLの活用方法をご提案させていただきます。

仮想実行環境による

SW開発評価プラン

120万円/年

HW・SW開発評価プラン

480万円/年

順次企画の上、アナウンスいたします。

開発規模・内容に応じて、開発支援企業体制の整備とプロジェクト管理をRVDCが担当いたします。費用は案件毎にご相談させていただきます。

お知らせ

お問い合わせ