Faster. Freer.

With RISC-V.

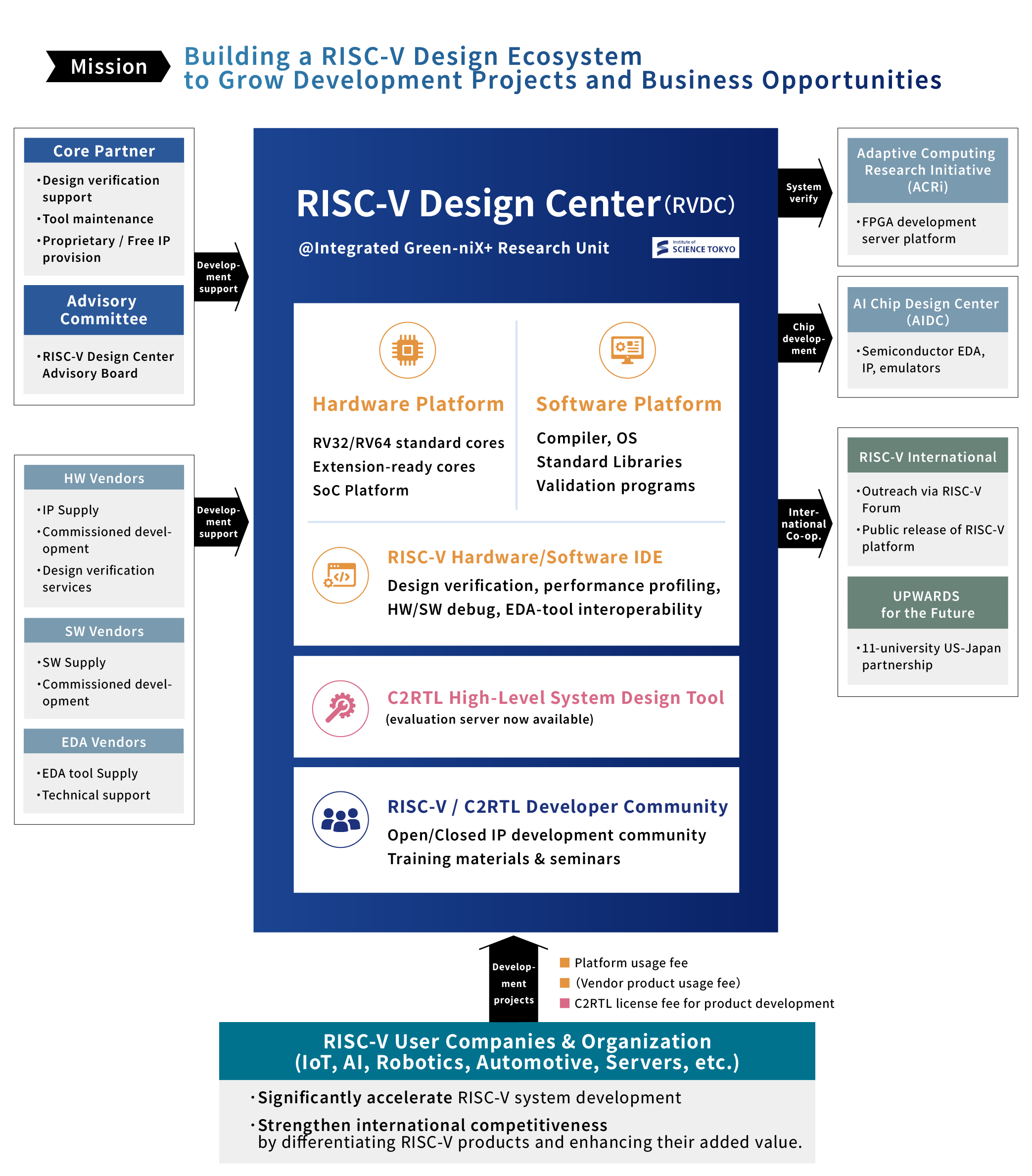

The RISC-V Design Center is

a Japan-based organization dedicated to

supporting the ecosystem of RISC-V development and design.

OVERVIEW

The RISC-V Design Center (RVDC) is a specialized organization based on the open RISC-V instruction set architecture. We collaborate with research institutions, advisors, and hardware/software vendors to provide RISC-V cores and SoC design assets to the broader industry. By promoting the adoption of innovative development methodologies, we aim to drive a new wave of product innovation within Japan’s semiconductor sector.

PROJECT OUTLINE

What is the RISC-V

Design Center?

The RISC-V Design Center (RVDC) provides a collaborative environment for learning and knowledge sharing, where participants can explore a new, highly efficient methodology for designing and verifying optimized RISC-V processors. This is achieved through the use of “C2RTL”—a cutting-edge high-level system design and verification platform—and the C-based implementation of RISC-V (5th generation RISC processors).

RVDC is a non-profit organization established within the Green-niX+ Research Unit at the Institute of Science Tokyo. It does not operate for commercial gain, and all participation fees listed are allocated solely to support RVDC’s operations.

- ・Phase 1 Project Period: August 2025 – July 2030

- Director, Phase 1 RISC-V Design Center: Tsuyoshi Isshiki

- ・Host Institution

- Integrated Green-niX+ Research Unit

- Location: Ookayama Campus Ishikawadai No.1 Bldg. 7F Room 754, Institute of Science Tokyo

- Address: I1-14, 2-12-1, Ookayama, Meguro-ku, Tokyo, 152-8552, Japan

- ・Operating Organization

- New System Vision Research and Development Institute

Collaborative Network

Core Partners

- Seiko Epson Corporation

- DENSO CORPORATION

Support Companies and Partners

Design Support Companies and Partners

- 株式会社NSVT